# APPLICATION NOTE

**JUNE 1983**

NA-038A

# EFB 7510 MODEM application principles

Augustin GIADIN Laboratoire d'applications

# INTRODUCTION

EFB7510 circuit of THOMSON-EFCIS offers a low-cost solution with a minimum of external components to requirements of MODEM applications compatible with CCITT V.23 and Bell 202 system recommendations. In fact, this circuit provides all modulation, demodulation and filtering functions required for FSK modulated data transmission via either switched telephone networks or leased data links. Control signals compatible with RS-232C of EIA and CCITT V.24 are also provided.

The present application note outlines the basic application principles of EFB7510 circuit. A typical application and its performances are also discussed.

THOMSON-EFCIS Integrated Circuits

# **FUNDAMENTALS**

The function of a MODEM is to allow via public telephone networks, a bi-directional data transfer between two distant computer-based systems. Figure 1 illustrates an example where a computer and a terminal are linked via two modems.

Operating principles are quite simple. The modem receives the data to be transmitted in digital form, converts it to analog signal (MODULATION) suitable for transmission over telephone lines. Inversely, it receives analog signals transmitted from distant station, converts them back to digital form (DEMODULATION) suitable for the computer.

FIGURE 1 - COMPUTER TO TERMINAL LINK VIA MODEMS

One of the most commonly employed techniques in digital signal transmission is FSK (Frequency Shift Keying) modulation. In this system, 2 frequencies f<sub>1</sub> and f<sub>2</sub> are used to represent digital levels "0" and "1" respectively.

In transmit mode, the modem receives binary data supplied for example by a UART (Universal Asynchronous Receiver Transmitter). When a logic "1" is detected, the modem outputs a sinewave signal of frequency f<sub>1</sub>. Likewise, for a logic "0" the modulator outputs a sinewave signal of frequency f<sub>2</sub>.

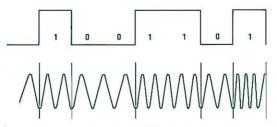

Binary digital data are so converted by the modem to analog signal containing 2 different frequencies of f<sub>1</sub> and f<sub>2</sub>, with of course, a continuity in phase (see figure 2). The analog signal so obtained, must be correctly filtered so as to eliminate the transmission of frequencies other than f<sub>1</sub> and f<sub>2</sub>.

Inversely, the demodulator receives via telephone line, a FSK modulated analog signal. This signal is first applied to a band-pass filter which removes all frequencies outside the modern reception band. The signal is then converted to digital form and applied to the computer system.

FIGURE 2 - FSK MODULATION

With a minimum of external components, the EFB7510 performs all of the functions just described. In addition to modulation and demodulation of signals, this circuit contains all necessary filtering for reception and transmission, while signals compatible with EIA - RS 232C and CCITT V.24 recommendations are also provided.

# **EFB7510 FUNCTIONAL DESCRIPTION**

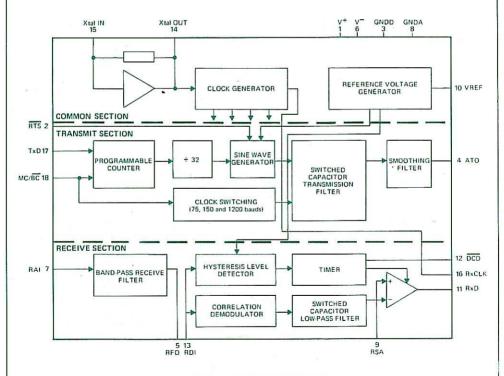

EFB7510 incorporates 4 main functional sections:

- A timing generator

- A modulator (transmitter)

- A demodulator (receiver)

- A reference voltage generator.

Figure 3 illustrates Circuit Block Diagram.

#### TIMING GENERATOR

This section uses a 3.579 MHz crystal clock in order to generate all the clock signals necessary for the circuit operation ie, for switched-capacitor filters, modulation, demodulation... It delivers also a 19.200 Hz clock which may be used by an external UART.

EFB7510's master clock may be generated either by connecting a 3.579 MHz crystal between Xtal IN and Xtal OUT pins or by applying an external CMOS clock to Xtal IN pin.

FIGURE 3 - EFB7510 BLOCK DIAGRAM

#### REFERENCE VOLTAGE GENERATOR

This section provides on VREF pin a regulated dc reference voltage independent of power supply values. This voltage is used to adjust the demodulator threshold transition levels by applying a fraction of VREF voltage to pin RSA, with an external potentiometer.

#### MODULATOR

The modulator receives binary digital data from a source such as a UART and converts the data to an analog signal using frequency shift keying (FSK) modulation. This signal is then transmitted over telephone networks through an appropriate interface.

The modulator is controlled by three input signals RTS, TxD and MC/BC.

Signal applied to MC/ $\overline{BC}$  (Main Channel/Back Channel) pin selects one-out of-3 possible pairs of transmission frequencies (see table 1). Each pair includes a high and a low frequency. For a selected MC/ $\overline{BC}$ , and while  $\overline{RTS}$  signal is low, the modulator outputs on pin ATO the low frequency signal when TxD (Transmit Data) is high ("1") and outputs the high frequency signal when TxD is low ("0").

In order to prevent the transmission of signals other than those falling within the transmitter frequency band, signals supplied by modulator sinewave generator are filtered prior to being output on pin ATO. Figure 4 illustrates the spectrum of signal output by EFB7510.

The three frequency pairs selected by  $MC/\overline{BC}$  signal correspond to transmission rates of 75, 150 and 1200 bauds (bits per second).

Note: Selecting TxD = "1" and  $MC/\overline{BC} = 0$ ,

RTS pin may be used to transmit the back channel employed in Bell 202 standards in amplitude modulation. Transmission rate is 5 bauds.

$\overline{RTS} = 1 : AT0 = analog ground$  $\overline{RTS} = 0 : AT0 = 390 Hz.$

When selecting  $MC/\overline{BC}=1$ , the performance of the modem subsystem can be tested on a local basis by using a local analog loop that loops the transmitted analog signal back to the receive analog input RAI.

TABLE 1 – TRANSMITTED FREQUENCIES OUTPUT VIA ATO PIN AND CONTROLLED BY

MC/RC & TxD INPUT SIGNALS

| MC/BC          | Transmission rate | TxD        | Transmitted frequency |

|----------------|-------------------|------------|-----------------------|

| GNDD           | 75 bauds          | "H"<br>"L" | 390 Hz<br>450 Hz      |

| V-             | 150 bauds         | "H"<br>"L" | 390 Hz<br>490 Hz      |

| V <sup>+</sup> | 1200 bauds        | "H"<br>"L" | 1300 Hz<br>2100 Hz    |

FIGURE 4 - SPECTRUM OF THE SIGNAL TRANSMITTED VIA ATO OUTPUT

#### RECEIVER

This section receives via telephone networks and through an appropriate interface circuit a FSK modulated analog signal. Its function is to convert the received signal into digital form. In addition, it supplies a control signal which corresponds to the level of the received analog signal (carrier detection).

# RECEIVE FILTER

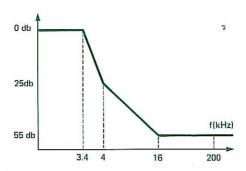

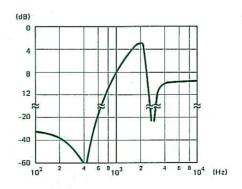

The received analog signal is first filtered by a band-pass filter whose function is to attenuate at maximum the frequency bands outside demodulator reception band. Figure 5 shows receive filter typical frequency response. From Figure 5, it is seen that while the modem is receiving at a rate of 1200 bauds the 1300 Hz and 2100 Hz frequencies - and is transmitting simultaneously on the back channel with the 390 Hz and 450 Hz frequencies - then, the frequencies of 390 Hz and 450 Hz are rejected in order to improve the performance of the demodulator.

Another important characteristic associated with the receive filter is the gain difference of 3 dB between 1300 Hz and 2100 Hz signal frequencies.

In fact, during the transmission of analog signals via telephone networks, high frequency signals are more attenuated than the low frequency signals. The receive filter provides a fixed compromise equalizer in order to correct this attenuation difference.

FIGURE 5 - RECEIVE FILTER TYPICAL FREQUENCY RESPONSE

#### DEMODULATOR

The signal output by the reception filter is delivered on pin RFO of the EFB7510. An external peaklimiting filter is necessary in order to eliminate noise generated by switched-capacitors and so as to suppress all offset voltages present at the demodulator input. A design example of peak-limiting filter is given later in the present document.

The signal supplied by peak-limiting filter is applied to RDI pin of EFB7510. This pin is connected to both correlation demodulator and to a carrier detection system. The function of the carrier detection circuitry is to provide on pin  $\overline{DCD}$  (Data Carrier Detect), information corresponding to the signal received on RDI input pin.  $\overline{DCD}$  output pin is generally connected to the UART  $\overline{DCD}$  input so as to provide the signalling of "carrier loss" during data reception.

Signal detection process performed by EFB7510 includes a threshold hysteresis with precise response time. Two threshold levels N1 and N2 are defined by internal comparators and result in a typical hysteresis ratio N1/N2 of 2.9 dB - while maximum detection level of N1 is fixed at 3 Vpp. Thus, the output  $\overline{DCD}$  is low while the peak-to-peak amplitude of the input signal on RDI pin exceeds N1.  $\overline{DCD}$  is high if this amplitude is lower than N2.

The signal detection system includes also a timer circuit the function of which is to control response times of the  $\overline{DCD}$  signal transition from one logic level to another. This response time depends on the threshold level associated with the amplitude of the signal received on RDI input (see technical specifications of EFB7510).

The correlation demodulator converts the signal at RDI input into a binary signal "1" if the former is a high frequency signal (2100 Hz) and into binary "0" if it is low frequency (1300 Hz). Principles employed in signal demodulation require a zero crossing detection of the signal. This fact emphasizes the importance of the external peak-limiting filter which must reject all offset voltages.

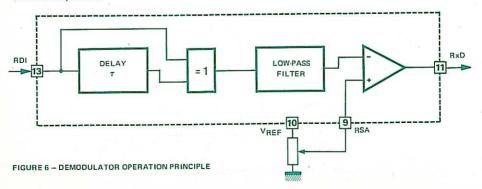

Figure 6 illustrates the operating principles of the correlation demodulator; which is to multiply the received signal by itself but delayed for a certain period

$$\tau = \frac{3}{4} \cdot \frac{1}{f_{\rm C}}$$

where  $f_C$  is the carrier frequency, which is also the centre frequency ( $f_C = 1700 \text{ Hz}$ ).

The signal at the demodulator output is first low-pass filtered and then applied to a comparator which provides the demodulated digital signal on RxD (Receive Data) pin. Comparator RSA input is used to adjust the signal frequency discrimination, thereby optimizing the demodulation performance. The voltage applied to this pin may be set externally by connecting a potentiometer to pin VREF through which the internally regulated reference voltage is output.

#### Note

Demodulator output signal is controlled by the carrier detection system. When the level of the received signal on RDI pin is insufficient,  $\{\overline{DCD} = 1\}$ , the output RxD remains in logic "1" irrespective of the received frequencies.

## **FFB7510 APPLICATION DESIGN EXAMPLE**

EFB7510 circuit performs all modulation, demodulation and filtering functions for the data transmission via public telephone networks.

Its operation requires a minimum number of external components for the implementation of peaklimiting filter, and external elements for telephone line interface system.

# **OPERATING CONDITIONS**

EFB7510 circuit is intended for the systems employing V.23 - CCITT or Bell 202 standards. In the present application note, we shall discuss only an EFB7510 based application example concerning V.23 standard.

One of the most important applications of this system is where a user's terminal is connected via telephone networks to a central computer for data acquisition or information retrieval purposes.

Public telephone networks are generally designed for voice transmission and as a consequence, have a frequency band of 300 Hz to 3400 Hz.

Consequently, the data transmission must be performed via a modem circuit which will convert the binary data into analog signals falling within the voice-frequency band.

Using public telephone networks is an economic solution since the required installations already exist on customer location. Nevertheless, telephone lines impose an important restriction which is data transmission rate. This is directly due to the channel bandwidth of the transmission lines. As a result, a bi-directional simultaneous transmission is only possible if the two transmission channels are adequately separated and fall within the frequency band authorized by the channel.

For a system employing the V.23 - CCITT standards, the EFB7510 allows for a simultaneous data exchange, as indicated below:

- On main channel, with a 1200-baud modulation rate. The two frequencies used are 1300 Hz and 2100 Hz.

- On back channel, with a 75-baud modulation rate. The two frequencies used are 390 Hz and 450 Hz

For the situation where EFB7510 is used to link a remote terminal to a host computer, the data transfer from the host computer to the terminal is done on the main channel and takes place at a much higher rate than in the opposite direction. The back channel is used by the remote terminal to communicate with the host computer. In general, these communications are short and consist of, for example, typed messages enterred from a keyboard.

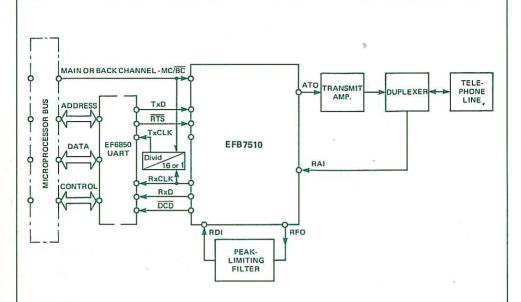

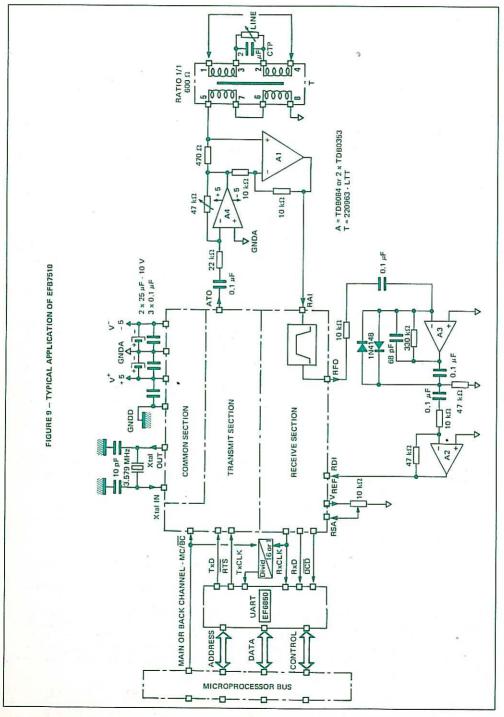

The EFB7510 application example which will be discussed below describes such system configuration. Figure 7 shows the application block diagram which consists of the following main section:

- EFB7510 circuit with its peak-limiting filter system.

- Telephone line interface.

- EF6850 UART, which acts as an interface between the microprocessor and the EFB7510.

# INTERFACING WITH EF6850 UART

EFB7510 and EF6850 circuits are interconnected by linking the following common pins together:

- TxD : Transmit data

- · RxD : Receive data

- RTS: Request to send

- DCD : Carrier detection.

For data reception at 1200 bauds, the 19.200 Hz clock generated by the EFB7510 can be applied directly to the UART RxCLK input. Since data transmission rate is 75 bauds, the 19.200 Hz clock must be divided by 16 to obtain the transmit clock for the UART TxCLK input. The EF6850 is then programmed with a clock divide ratio of ÷ 16.

FIGURE 7 - APPLICATION BLOCK DIAGRAM

### DUPLEXER

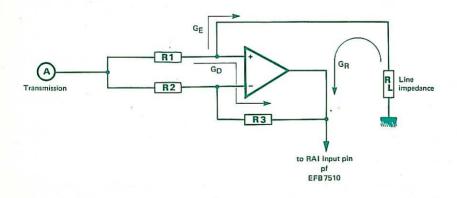

The duplexer is intended to provide an interface between the EFB7510 and the telephone system. Since data flow is bi-directional on the telephone line, the duplexer must allow the received signal to pass on the RAI input, properly couple the transmitted signal onto the line, minimize the local transmitted level towards the receiver, and properly terminate the transmission line.

Figure 8 gives an example of duplexer design.

FIGURE 8 - DUPLEXER REALIZATION

The gain from duplexer input A to the telephone line is:

$$GE = \frac{RL}{RL + R1}$$

where R<sub>L</sub> is the line impedance and considered to be nominally 600  $\Omega$  resistive. For a perfect impedance matching, R<sub>1</sub> must be equal to R<sub>L</sub>.

Thus,  $R_1 = R_1 = 600 \Omega$  and  $G_E = 0.5$ .

The gain from duplexer input A to EFB7510 input RAI is:

$$G_D = -\frac{R_3}{R_2} + (1 + \frac{R_3}{R_2}) (\frac{R_L}{R_1 + R_1})$$

In order to eliminate the transmitted signal to the modem receive input, it is desired that  $G_D = 0$ .

With R1 = R1:

$$G_D = 0 = -\frac{R_3}{R_2} + \frac{1}{2} \left(1 + \frac{R_3}{R_2}\right)$$

Thus,  $R_3 = R_2$

Since all impedances except the line impedance R<sub>L</sub> can be accurately controlled, the duplexer rejection performance depends directly on R<sub>L</sub>. In practice, due to the variations of the line impedance which is not in reality a pure resistive load, an attenuation of around – 10 dB is assumed to be provided by the duplexer.

The gain from the line transformer to the EFB7510 receive input is:

$$G_R = 1 + \frac{R_3}{R_2}$$

With  $R_3 = R_2 : G_R = 2$ , ie + 6 dB.

#### PEAK-LIMITING FILTER

The reception performance of the EFB7510 depends directly on the duplexer and the peak-limiting filter. The peak-limiting circuit is placed between the RFO output pin of the reception filter and the demodulator input RDI. It must perform the following functions:

- Eliminate all frequencies outside the demodulation frequency band, with band-pass filter.

- Appropriate signal amplification as a function of the signal level received from the telephone line, for the carrier detection system.

An example of the peak-limiting circuit design is given in Figure 9.

The first operational amplifier performs simultaneously the tasks of signal amplification, low-pass filter and peak-limiting (using 2 signal diodes).

The output of this amplifier is applied to a second operational amplifier which provides an adjustable overall system gain.

The overall gain of the peak-limiting filter must be linear for RDI input signal levels lower than the detection threshold N<sub>1</sub> (3Vpp). For higher signal levels, the diode peak-limiting system limits the amplified signal so as to prevent the saturation of the amplifier. Consequently, no dc component (offset voltage) is injected into the amplified signal. This characteristic is of utmost importance, since the principles employed in EFB7510 circuit rely on the zero-crossing detection of the signal received on RDI input.

THOMSON-EFCIS Integrated Circuits

FIGURE 10 - RECEIVE SECTION

# GAIN CALCULATION OF THE RECEIVE SECTION (See Figure 9 & 10)

The signal detection system of EFB7510 operates on two detection threshold levels of  $N_1$  and  $N_2$ . The gain of various filters and amplifiers associated with the receive section between the line transformer output and the RDI input of the circuit must be adjusted according to the level range of the signal received through telephone network. A calculation example is given below, where it has been assumed that the signal levels received by the line transformer, have values ranging from 0 dBm to - 44 dBm.

The receive section consists of:

- the duplexer

- EFB7510 receive filter

- · external peak-limiting filter.

The gain of the duplexer in receive mode is :  $G_R = 2$ , ie+ 6 dB. Average signal attenuation introduced by the receive filter is 3 dB. The upper threshold level of the system is fixed at 3 Vpp which is+ 2.7 dBm. This threshold level must correspond to the lowest signal level received by the line transformer of – 44 dBm. Consequently, the gain  $G_{FE}$  of the peak-limiting filter is given as follows:

$$-44 + 6 - 3 + GFE = +2.7 dBm$$

thus GFE =  $43.7 \text{ dB} \simeq 153$ .

#### Note:

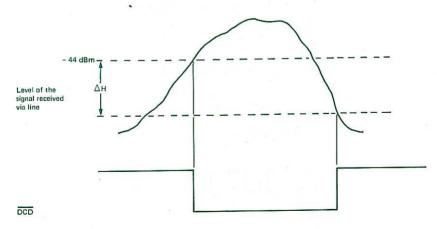

Due to the hysteresis employed in the carrier detection system, the output  $\overline{DCD}$  is only active (active low) if the signal level received via line exceeds – 44 dBm. The signal  $\overline{DCD}$  will pass to logic level "1" (loss of carrier) only if the level of received signal is lower than – 44 dBm –  $\Delta_H$ , where  $\Delta_H$  is the hysteresis ratio N<sub>1</sub>/N<sub>2</sub> of the signal detector (see technical specifications of EFB7510).

FIGURE 11

Figure 11 shows how  $\overline{DCD}$  signal changes state as a function of the signal level, if the response times associated with the timer circuit are ignored. The hysteresis value  $\Delta_H$  of the carrier detection system is generally between 2 dB and 4 dB, so as to comply with CCITT V.23 standard requirements.

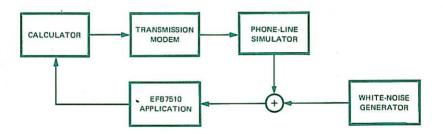

#### APPLICATION PERFORMANCES

In this section, typical performances obtained in a EFB7510 based application will be discussed. The test configuration is given by Figure 12 and consists of :

- EFB7510 based application described previously.

- A telephone line simulator and a white-noise generator.

- · A reference MODEM for data transmission on the main channel.

- A calculator for the generation of test pattern (511-bit random) and for the measurement of distortion and bit error rates.

For every measurement, the calculator generates pseudo-random sequences of 511 bits. These binary digital data are FSK modulated by the transmission modem, and the analog signal output by the modem is applied to the telephone line simulator. A desired value of signal-to-noise ratio is obtained with the white-noise generator.

The signal output by the simulator is applied to the EFB7510 based application. Digital signal demodulated by the modem is analyzed by the calculator which compare the transmitted bits with the received bits. Since transmitted signals are subject to a certain delay through various elements of the test loop, the calculator is equipped with a clock regeneration system which enables a correct synchronization with the digital signal received from EFB7510.

FIGURE 12 - TEST CONFIGURATION

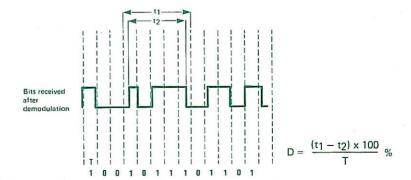

FIGURE 13 - ISOCHRONOUS DISTORTION

#### TEST CONDITIONS

Reception level on EFB7510-based card: variable, according to line type

Transmission level on back channel : −2 dBm to −10 dBm

Pseudo-random sequence of 511 bits : in accordance with V.52 requirements of CCITT.

Before measuring isochronous distortion and bit error rates associated with various types of lines, the EFB7510 demodulator is adjusted so as to obtain a zero bias distortion. This is done by transmitting with the reference modern an alternating sequence of "1s" and "0s" on a flat line. The potentiometer connected between VREF and RSA pins is then adjusted to obtain a correct bit interval at the EFB7510 Receive Data RxD pin.

#### ISOCHRONOUS DISTORTION

When continuous digital bit streams that have been transmitted over analog lines are demodulated, their actual bit transitions seldom fall exactly on integer multiples of the expected bit period. The ratio of the maximum difference between real bit transitions and integer bit transitions to the bit period is called isochronous distortion. With reference to figure 13, if T is the ideal bit period, isochronous distortion D is defined as the amount of jitter displacement (t<sub>1</sub> - t<sub>2</sub>), of the real demodulated bit stream divided by T. As with most distortion measures, the isochronous ratio is generally multiplied by 100 and referred to as a percent.

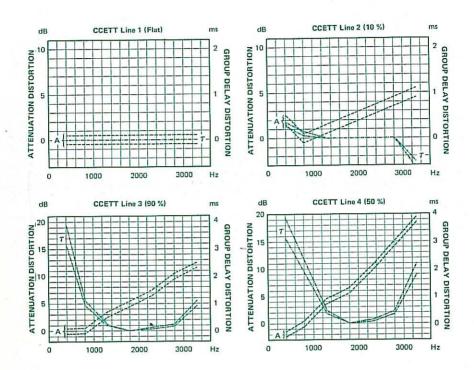

For frequency-shift-keying modems, isochronous distortion is essentially due to the group delay and attenuation response of the telephone line, and to the various filters and circuitry used in the demodulation process. Table 2 gives typical isochronous distortion values achieved by the EFB7510, for various lines whose characteristics are given in Annex 1. These values depend on the test configuration and are supplied for information only.

TABLE 2

| Line        | Distortion |  |

|-------------|------------|--|

| N° 1 (flat) | 10 %       |  |

| N° 2        | 14 %       |  |

| N° 3        | 14 %       |  |

| N° 4        | 12 %       |  |

# BIT ERROR RATE VERSUS WHITE-NOISE

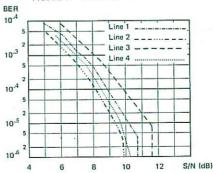

Figure 14 depicts typical bit error rates versus white-noise for various lines whose characteristics are given in annex 1.

ANNEX 1

# Characteristics of the lines used.

# FIGURE 14 - TYPICAL BIT ERROR RATE

Information contained in this application note has been carefully checked and is believed to be entirely reliable.

However, no responsibility is assumed for inaccuracies.

Printed in France